尽管基于二维材料及其范德华异质结构在电子学领域的应用取得了飞速发展,但最大的挑战仍然是找到需要大量使用这些材料的“杀手级应用”。晶体管技术一直是现代电子技术的基础,降低晶体管器件的功耗始终是技术革新的驱动力。

近日,清华大学精密仪器系李黄龙副教授(通讯作者)及其博士后吕娟(第一作者)在Advanced Materials 上发表论文,研究了二维异质结在低功耗冷源超陡亚阈值摆幅晶体管中的应用潜力。他们通过材料模拟和器件建模,证明大量二维金属源材料(包括石墨烯、过渡金属硫化物TMDs、过渡金属碳化物MXenes)可以自然地满足新型冷源晶体管的构建需求,即具备超指数减小的热载流子分布函数n(E)。文中强调,这一特性结合二维范德华金属-半导体界面的非化学键结合(减轻费米能级钉扎效应从而实现栅极可调控的界面势垒高度)可以使二维金属:半导体异质结成为冷源晶体管的理想材料基础。

新型冷源场效应晶体管(Science, 2018, 361, 387)改进了原有的热输运机制,依靠冷源注入实现了陡峭的亚阈值摆幅 (SS) 低功耗特性。其主要原理是利用了源极金属热载流子态密度随能量递减的这一特点促使源极热载流子的分布函数形成超指数减小的趋势,这有效地抑制了玻尔兹曼分布热尾巴在能量较高处(沟道势垒上方)对关态电流的贡献,从而将SS值降低至60 mV/decade以下。

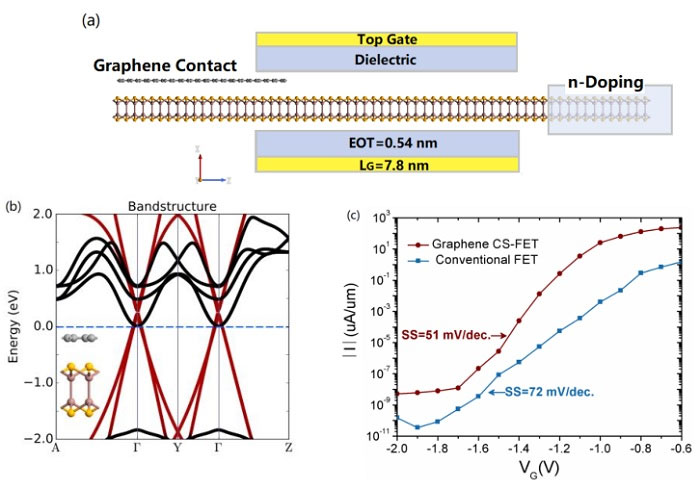

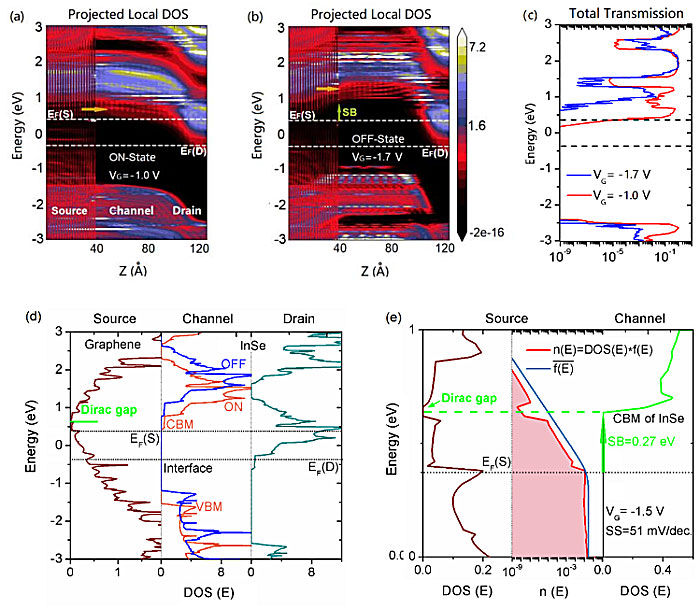

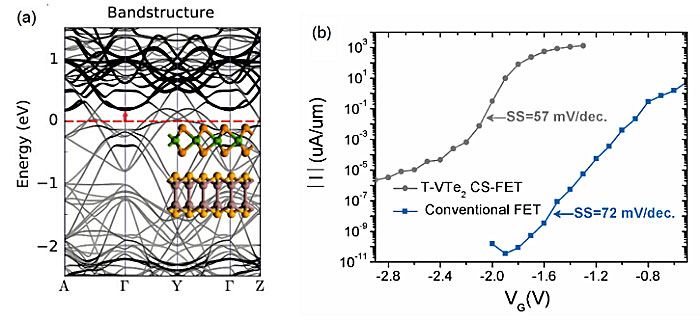

该工作基于石墨烯(本征和掺杂情况)等冷源材料与单层 InSe沟道构成的n型器件进行测试仿真,发现石墨烯冷源与InSe异质结界面形成近似的n型欧姆接触,且石墨烯在与InSe接触后自发地形成了p型掺杂状态,这就使本征石墨烯的态密度在费米能级以上的一部分能量区间内自然地形成了随能量增加而减小的趋势。模拟得到的转移特性曲线显示与源漏n型掺杂的传统InSe晶体管相比,石墨烯冷源晶体管对亚阈值漏电有明显的抑制作用,出现的最陡峭亚阈值摆幅为51 mV /decade。

图1. (a) 基于单层InSe的n型石墨烯冷源晶体管的侧视图。(b)石墨烯-InSe异质结的能带结构。石墨烯以及InSe贡献的电子态分别由红色和黑色曲线标记。(c)石墨烯冷源晶体管和传统晶体管的转移特性曲线对比。

图2. 石墨烯冷源器件的投影态密度图 (a)开态,(b)关态。(c)输运谱对比图。(d)原子态密度图。(e)态密度DOS(E)和载流子分布函数n(E)在SS最小值处的放大图。蓝色线代表随能量呈线性减小的玻尔兹曼分布函数。

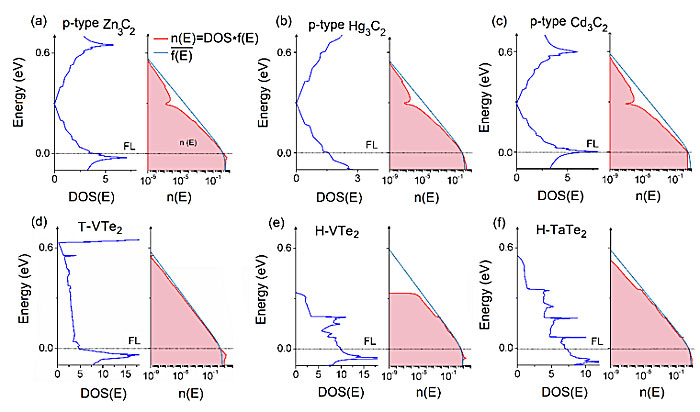

该工作发现除了石墨烯以外,其他二维材料,包括金属碳化物和过渡金属硫属化合物同样具备冷源材料的特点。例如,p型掺杂的MXenes具有类狄拉克能量色散关系,因此费米能级以上态密度是能量的递减函数,热载流子分布以超指数形式减少。TMDs的态密度整体上具有随能量增加而衰减的趋势,这些特性可以有效地抑制玻尔兹曼热分布尾巴附近的载流子输运。

图3. 态密度DOS(E)和载流子分布函数n(E)。p型掺杂的(a) Zn3C2, (b) Hg3C2, (c) Cd3C2。过渡金属硫化合物(d)T相VTe2, (e)H相VTe2, (f) H相TaTe2。

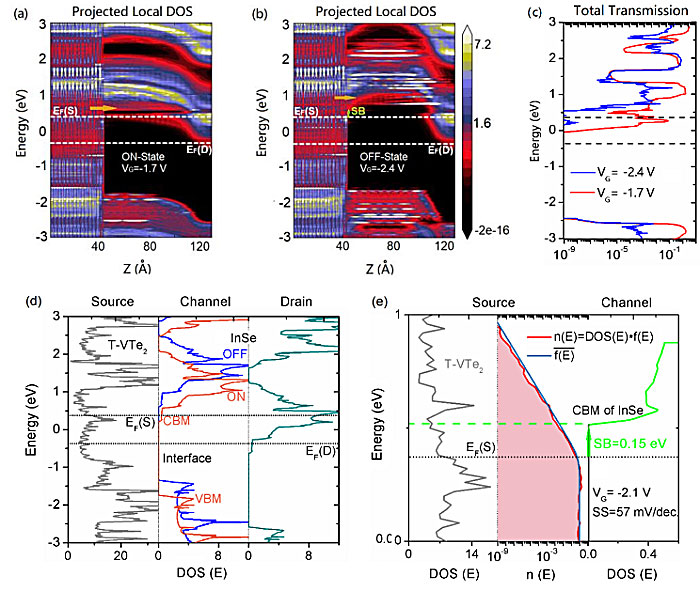

如研究者的预测,VTe2(T相和H相)、Cd3C2和H-TaTe2构成的冷源器件在仿真中均获得低于60 mV/decade的SS值。

图4. (a) InSe和T-VTe2异质结的能带结构。单层InSe和T-VTe2贡献的电子态分别由黑线和灰线标记。(b) T-VTe2冷源晶体管和传统晶体管的转移特性曲线对比。

器件的开/关态的投影态密度图表明源和沟道界面的肖特基势垒可以通过栅极电压进行有效地调控。从原子态密度的放大图中可以观察到T-VTe2冷源的载流子分布函数以超指数的形式减小,这使SS降至低于60 mV/decade。此外,VTe2还具有复杂丰富的相变现象,这说明二维材料大家族不仅可以为冷源晶体管的设计提供丰富的原材料,还可以提供相变自由度。二维材料的相变和多晶态工程可以在不引入其它元素的条件下改变材料的性能,具有一定的应用价值。

图5. T-VTe2冷源器件的投影态密度图 (a)开态,(b)关态。(c)输运谱对比图。(d)原子态密度图。(e)态密度DOS(E)和载流子分布函数n(E)在SS最小值处的放大图。蓝色线代表随能量呈线性减小的玻尔兹曼分布函数。

此外,从态密度工程的角度出发,实现具有陡峭SS特性、低关态电流和高开态电流的冷源晶体管以及探索冷源器件中金属-半导体同质结的同素异相集成都是未来值得进一步研究的内容。这项工作不仅为低功耗冷源器件的设计提供了新的材料方案,同时极大地扩展了二维材料的应用潜力。

原文(扫描或长按二维码,识别后直达原文页面,或点此查看原文):

A New Opportunity for 2D van der Waals Heterostructures: Making Steep‐Slope Transistors

Juan Lyu, Jing Pei, Yuzheng Guo, Jian Gong, Huanglong Li

Adv. Mater., 2019, DOI: 10.1002/adma.201906000

导师介绍

清华大学精密仪器系李黄龙副教授团队致力于低功耗、高速度、新架构芯片的元器件和材料研究,近年来在神经形态器件(Truly Concomitant and Independently Expressed Short- and Long-Term Plasticity in a Bi2O2Se-Based Three-Terminal Memristor, Adv. Mater., 2019, 31, 1805769) 和超陡亚阈值摆幅晶体管(A New Opportunity for 2D van der Waals Heterostructures: Making Steep-Slope Transistors, Adv. Mater., 2019, DOI: 10.1002/adma.201906000)方面取得重要的阶段性突破。课题组常年招聘实验(神经形态微纳电子器件、基于二维材料的电子器件、非易失存储器等)和理论(使用ATK, CASTEP, VASP等对电子器件和电子材料进行研究)方向的优秀博士后、联培生和参与研究训练的本科生,以及实验方向的博士生。

https://www.x-mol.com/university/faculty/60804

0

0